AIGC动态欢迎阅读

原标题:中科大/华为诺亚出手!芯片性能≠布局评分,EDA物理设计框架全面开源

关键字:报告,华为,布局,算法,芯片

文章来源:量子位

内容字数:0字

内容摘要:

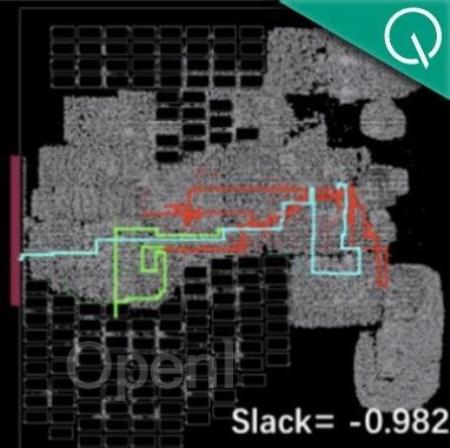

ChipBench团队 投稿量子位 | 公众号 QbitAI芯片物理布局,有了直指性能指标的新测评标准!

中科大MIRA Lab和华为诺亚方舟实验室联合发布了新的评估框架和数据集,而且完全开源。

有了这套标准,布局指标与最终的端到端性能不一致、得分高而PPA性能却偏低的问题,就有望得到解决了。

在芯片设计当中,电子设计自动化(EDA)是至关重要的一环,在业界被称为“芯片之母”,而芯片物理布局(Placement)又是其中的关键步骤。

芯片物理布局问题是一个NP-hard问题,人们尝试着通过AI来进行这项工作,但缺乏一个有效的评测标准。

传统的评估尺度——代理指标虽然易于计算,但常常与芯片最终的端到端性能存在显著差异。

为了弥补这一鸿沟,中科大MIRA Lab和华为诺亚方舟实验室联合发布了这个名为ChiPBench的评估框架,以及相关数据集。

随着ChiPBench的上线,作者也发现了当前芯片布局算法存在很多不足,提醒相关研究人员是时候研发新算法了。

芯片设计流程面临挑战根据“摩尔定律”,集成电路(IC)的规模发生了指数级增长,对芯片设计带来了前所未有的挑战。

为了应对这种日益增长的复杂

原文链接:中科大/华为诺亚出手!芯片性能≠布局评分,EDA物理设计框架全面开源

联系作者

文章来源:量子位

作者微信:

作者简介:

© 版权声明

文章版权归作者所有,未经允许请勿转载。

相关文章

暂无评论...

粤公网安备 44011502001135号

粤公网安备 44011502001135号